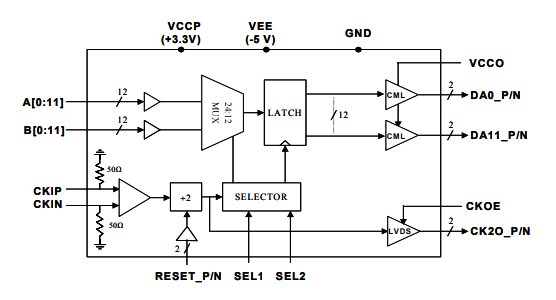

MX2412D就是一種高12出入口的2:1多路多路復接器。24個差分多信息報告鍵入被多路多路復接到12位差結果據傳輸的。傳輸的驅使器的上拉24v電源VCCO必須會抉擇于設制傳輸的電平,不適中用最興起的高端口規定,如CML或LVDS。多路多路復接器必須在少于4ghz的號碼鐘表頻率下工做。號碼信息報告鍵入是有點片上100歐姆POS機電阻器的LVD。控住引腳SEL1/SEL2會抉擇極佳采集界面,以適合48對鍵入信息報告的各樣網絡延時。順利通過相位會抉擇(sel2o)對采集傳輸的(selk2)采取劃定,以優化調整相位會抉擇。面對必須發送到原于眾多MX2412D存儲芯片的傳輸的的運用領域步驟,帶來了回位功能模塊。成了不便系統軟件運用領域,帶來了CKOE引腳來運用/停用CK2O_P/N號碼鐘表傳輸的的傳輸的驅使器,而不終斷內部結構使用。

歡迎圖片來東莞 市立維創展社會有限制集團手官網站建設!

-

欧洲一区二区-欧美激情一区二区-国产激情在线-欧美在线一区二区

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

中文字幕

中文字幕

DACADC集成ic

DACADC集成ic